Now Reading: AMD pregăteşte următorul pas pentru Ryzen: 3D V-Cache extins şi la memoria L2

-

01

AMD pregăteşte următorul pas pentru Ryzen: 3D V-Cache extins şi la memoria L2

AMD pregăteşte următorul pas pentru Ryzen: 3D V-Cache extins şi la memoria L2

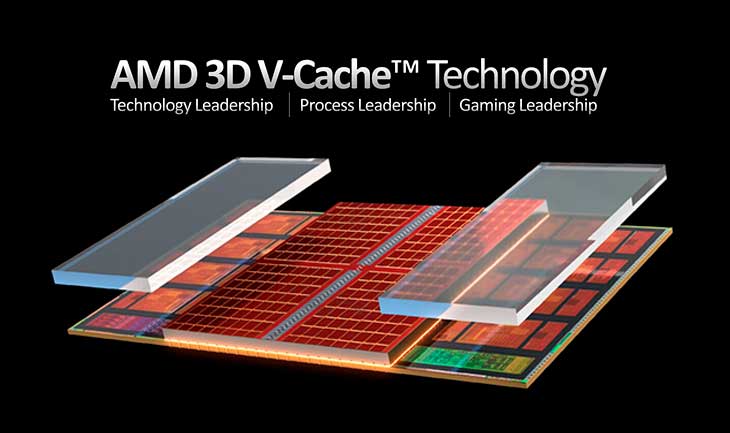

AMD a brevetat o nouă abordare menită să împingă şi mai departe performanţele procesoarelor Ryzen, prin extinderea tehnologiei 3D V-Cache dincolo de memoria L3. Mai exact, inginerii AMD explorează o metodă prin care şi memoria cache L2 ar putea beneficia de un design 3D, fără a penaliza semnificativ latenţele sau costurile de fabricaţie.

Până acum, tehnologia 3D V-Cache a evoluat în două etape clare. Prima generaţie a dublat capacitatea cache-ului L3 prin adăugarea unui cip de memorie stivuit direct peste pastila procesorului. A doua generaţie a rafinat soluţia, mutând cipul de memorie sub pastila principală pentru a îmbunătăţi disiparea termică. Cel mai recent brevet sugerează însă o a treia etapă, mult mai ambiţioasă, în care AMD ar adăuga un nou nivel de memorie cache stivuită, vizând de această dată cache-ul L2, un element critic pentru performanţa procesoarelor moderne, dar extrem de costisitor atunci când este integrat direct în siliciu.

Deşi memoria L3 este considerată cache-ul de ultim nivel, care face legătura dintre procesor şi memoria RAM, memoria L2 joacă un rol chiar mai sensibil. Aici sunt stocate datele folosite activ de nucleele de procesare, iar latenţele extrem de mici sunt esenţiale. Din acest motiv, cache-ul L2 este sever limitat ca dimensiune, iar orice creştere a capacităţii poate aduce câştiguri importante în aplicaţii complexe şi foarte sensibile la întârzierile arhitecturii de memorie.

Pentru a ataca această limitare, AMD a brevetat un concept numit „Balanced Latency Stacked Cache”, un design care promite reducerea întârzierilor de acces şi o eficienţă energetică mai bună pentru viitoarele procesoare Ryzen X3D. Comparativ cu procesoarele convenţionale, care folosesc cache planar integrat în aceeaşi pastilă de siliciu, soluţiile cu cache 3D pot oferi latenţe şi consum energetic mai mici, ceea ce se traduce direct în performanţe superioare.

Conform brevetului, noul design de cache L2 stivuit ar reduce latenţa de acces pentru o memorie L2 de 1 MB de la aproximativ 14 cicluri la doar 12 cicluri. Diferenţa poate părea modestă la prima vedere, însă în arhitectura procesoarelor fiecare ciclu contează. În contextul în care o memorie L2 obişnuită poate avea latenţe între 10 şi 50 de cicluri, o astfel de optimizare este semnificativă.

Din punct de vedere tehnic, implementarea presupune comunicarea dintre pastilele de siliciu suprapuse prin trasee verticale din cupru (TSV) şi conexiuni de tip bond pad, toate rutate prin centrul zonei de memorie L2. Această abordare minimizează distanţele fizice de comunicare şi creează o structură simetrică, „echilibrată”, care ajută la sincronizarea accesului la date şi la reducerea variaţiilor de latenţă. De aici provine şi denumirea brevetului, „Balanced Latency Stacked Cache”.

Este important de subliniat că, pentru moment, vorbim doar despre un concept descris într-un brevet aflat în curs de aprobare. Nu există o confirmare că această tehnologie va ajunge într-un viitor apropiat în procesoare comerciale. Totuşi, direcţia indicată de AMD sugerează că evoluţia 3D V-Cache este departe de a se fi încheiat şi că generaţiile viitoare de Ryzen ar putea beneficia de câştiguri consistente de performanţă prin inovaţii la nivelul memoriei cache.